ЫцзХ PCB аХКХЧаЛЛЫйЖШВЛЖЯдіГЄЃЌЕБНёЕФ PCB ЩшМЦГЇЩЬашвЊРэНтКЭПижЦ PCB МЃЯпЕФзшПЙЁЃЯргІгкЯжДњЪ§зжЕчТЗНЯЖЬЕФаХКХДЋЪфЪБМфКЭНЯИпЕФЪБжгЫйТЪЃЌPCB МЃЯпВЛдйЪЧМђЕЅЕФСЌНгЃЌЖјЪЧДЋЪфЯпЁЃ

дкЪЕМЪЧщПіжаЃЌашвЊдкЪ§зжБпМЪЫйЖШИпгк1nsЛђФЃФтЦЕТЪГЌЙ§300MhzЪБПижЦМЃЯпзшПЙЁЃPCB МЃЯпЕФЙиМќВЮЪ§жЎвЛЪЧЦфЬиадзшПЙЃЈМДВЈбиаХКХДЋЪфЯпТЗДЋЫЭЪБЕчбЙгыЕчСїЕФБШжЕЃЉЁЃгЁжЦЕчТЗАхЩЯЕМЯпЕФЬиадзшПЙЪЧЕчТЗАхЩшМЦЕФвЛИіживЊжИБъЃЌЬиБ№ЪЧдкИпЦЕЕч ТЗЕФPCBЩшМЦжаЃЌБиаыПМТЧЕМЯпЕФЬиадзшПЙКЭЦїМўЛђаХКХЫљвЊЧѓЕФЬиадзшПЙЪЧЗёвЛжТЃЌЪЧЗёЦЅХфЁЃетОЭЩцМАЕНСНИіИХФюЃКзшПЙПижЦгызшПЙЦЅХфЃЌБОЮФжиЕуЬжТлзшПЙПижЦКЭЕўВуЩшМЦЕФЮЪЬтЁЃ

зшПЙПижЦ

зшПЙПижЦ(eImpedance Controling)ЃЌЯпТЗАхжаЕФЕМЬхжаЛсгаИїжжаХКХЕФДЋЕнЃЌЮЊЬсИпЦфДЋЪфЫйТЪЖјБиаыЬсИпЦфЦЕТЪЃЌЯпТЗБОЩэШєвђЪДПЬЃЌЕўВуКёЖШЃЌЕМЯпПэЖШЕШВЛЭЌвђЫиЃЌНЋЛсдьГЩзшПЙжЕЕУБфЛЏЃЌЪЙЦфаХКХЪЇецЁЃЙЪдкИпЫйЯпТЗАхЩЯЕФЕМЬхЃЌЦфзшПЙжЕгІПижЦдкФГвЛЗЖЮЇжЎФкЃЌГЦЮЊЁАзшПЙПижЦЁБЁЃ

PCB МЃЯпЕФзшПЙНЋгЩЦфИагІКЭЕчШнадЕчИаЁЂЕчзшКЭЕчЕМЯЕЪ§ШЗЖЈЁЃгАЯьPCBзпЯпЕФзшПЙЕФвђЫижївЊга: ЭЯпЕФПэЖШЁЂЭЯпЕФКёЖШЁЂНщжЪЕФНщЕчГЃЪ§ЁЂНщжЪЕФКёЖШЁЂКИХЬЕФКёЖШЁЂЕиЯпЕФТЗОЖЁЂзпЯпжмБпЕФзпЯпЕШЁЃPCB зшПЙЕФЗЖЮЇЪЧ 25 жС120 ХЗФЗЁЃ

дкЪЕМЪЧщПіЯТЃЌPCB ДЋЪфЯпТЗЭЈГЃгЩвЛИіЕМЯпМЃЯпЁЂвЛИіЛђЖрИіВЮПМВуКЭОјдЕВФжЪзщГЩЁЃМЃЯпКЭАхВуЙЙГЩСЫПижЦзшПЙЁЃPCB НЋГЃГЃВЩгУЖрВуНсЙЙЃЌВЂЧвПижЦзшПЙвВПЩвдВЩгУИїжжЗНЪНРДЙЙНЈЁЃЕЋЪЧЃЌЮоТлЪЙгУЪВУДЗНЪНЃЌзшПЙжЕЖМНЋгЩЦфЮяРэНсЙЙКЭОјдЕВФСЯЕФЕчзгЬиадОіЖЈЃК

PCBДЋЪфЯпжївЊгаСНжжаЮЪНЃКЮЂДјЯпЃЈMicrostripЃЉгыДјзДЯпЃЈStriplineЃЉЁЃ

ЮЂДјЯпЃЈMicrostripЃЉЃК

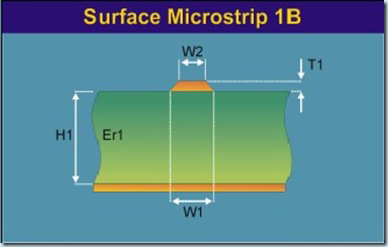

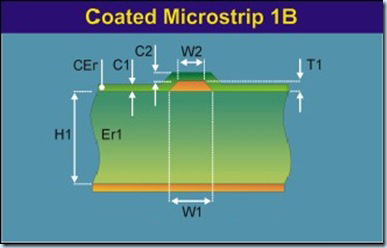

ЮЂДјЯпЪЧвЛИљДјзДЕМЯпЃЌжИжЛгавЛБпДцдкВЮПМЦНУцЕФДЋЪфЯпЃЌЖЅВПКЭВрБпЖМЦижУгкПеЦјжаЃЈвВПЩЩЯЗѓЭПИВВуЃЉЃЌЮЛгкОјдЕГЃЪ§ Er ЯпТЗАхЕФБэУцжЎЩЯЃЌвдЕчдДЛђНгЕиВуЮЊВЮПМЁЃШчЯТЭМЫљЪОЃК

зЂвтЃКдкЪЕМЪЕФPCBжЦдьжаЃЌАхГЇЭЈГЃЛсдкPCBАхЕФБэУцЭПИВвЛВуТЬгЭЃЌвђДЫдкЪЕМЪЕФзшПЙМЦЫужаЃЌЭЈГЃЖдгкБэУцЮЂДјЯпВЩгУЯТЭМЫљЪОЕФФЃаЭНјааМЦЫуЃК

ДјзДЯпЃЈStriplineЃЉЃК

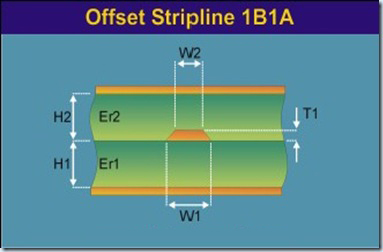

ДјзДЯпЪЧжУгкСНИіВЮПМЦНУцжЎМфЕФДјзДЕМЯпЃЌШчЯТЭМЫљЪОЃЌH1КЭH2ДњБэЕФЕчНщжЪЕФНщЕчГЃЪ§ПЩвдВЛЭЌЁЃ

ЩЯЪіСНИіР§згжЛЪЧЮЂДјЯпКЭДјзДЯпЕФвЛИіЕфаЭЪОЗЖЃЌОпЬхЕФЮЂДјЯпКЭДјзДЯпгаКмЖржжЃЌШчИВФЄЮЂДјЯпЕШЃЌЖМЪЧИњОпЬхЕФPCBЕФЕўВуНсЙЙЯрЙиЁЃ

гУгкМЦЫуЬиадзшПЙЕФЕШЪНашвЊИДдгЕФЪ§бЇМЦЫуЃЌЭЈГЃЪЙгУГЁЧѓНтЗНЗЈЃЌЦфжаАќРЈБпНчдЊЫиЗжЮідкФкЃЌвђДЫЪЙгУзЈУХЕФзшПЙМЦЫуШэМўSI9000ЃЌЮвУЧЫљашзіЕФОЭЪЧПижЦЬиадзшПЙЕФВЮЪ§ЃК

ОјдЕВуЕФНщЕчГЃЪ§ErЁЂзпЯпПэЖШW1ЁЂW2ЃЈЬнаЮЃЉЁЂзпЯпКёЖШTКЭОјдЕВуКёЖШHЁЃ

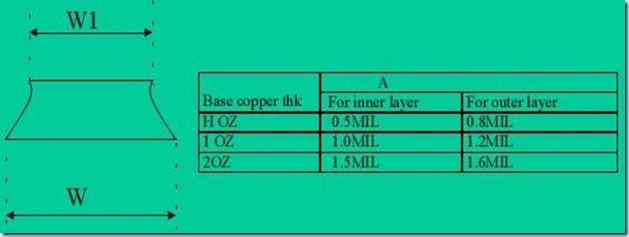

ЖдгкW1ЁЂW2ЕФЫЕУїЃК

ДЫДІЕФW=W1ЃЌW1=W2.

ЙцдђЃКW1=W-A

WЁЊ-ЩшМЦЯпПэ

AЁЊЈCEtch loss (МћЩЯБэ)

зпЯпЩЯЯТПэЖШВЛвЛжТЕФдвђЪЧЃКPCBАхжЦдьЙ§ГЬжаЪЧДгЩЯЕНЯТЖјИЏЪДЃЌвђДЫИЏЪДГіРДЕФЯпГЪЬнаЮЁЃ

зпЯпКёЖШTгыИУВуЕФЭКёгаЖдгІЙиЯЕЃЌОпЬхШчЯТЃК

ЭКё

COPPER THICKNESS

Base copper thk For inner layer For outer layer

H OZ 0.6mil 1.8mil

1 OZ 1.2MIL 2.5MIL

2 OZ 2.4MIL 3.6MIL

ТЬгЭКёЖШЃК

*вђТЬгЭКёЖШЖдзшПЙгАЯьНЯаЁЃЌЙЪМйЖЈЮЊЖЈжЕ0.5milЁЃ

ЮвУЧПЩвдЭЈЙ§ПижЦетМИИіВЮЪ§РДДяЕНзшПЙПижЦЕФФПЕФЃЌЯТУцвдАВЮЌЕФЕзАхPCBЮЊР§ЫЕУїзшПЙПижЦЕФВНжшКЭSI9000ЕФЪЙгУЃК

ЕзАхPCBЕФЕўВуЮЊЯТЭМЫљЪОЃК

![PCBзшПЙПижЦ B)01KR{XJCBYJX]P)T[3K]2](http://www.hqpcb.com/Public/Theme/Admin/Dwz/js/ueditor/php/upload/49681407486072.jpg)

ЕкЖўВуЮЊЕиЦНУцЃЌЕкЮхВуЮЊЕчдДЦНУцЃЌЦфгрИїВуЮЊаХКХВуЁЃ

ИїВуЕФВуКёШчЯТБэЫљЪОЃК

|

Layer Name

|

Type

|

Material

|

Thinkness

|

Class

|

|

SURFACE

|

AIR

|

|

|

|

TOP

|

CONDUCTOR

|

COPPER

|

0.5 OZ

|

ROUTING

|

|

DIELECTRIC

|

FR-4

|

3.800MIL

|

|

|

L2-INNER

|

CONDUCTOR

|

COPPER

|

1 OZ

|

PLANE

|

|

DIELECTRIC

|

FR-4

|

5.910MIL

|

|

|

L3-INNER

|

CONDUCTOR

|

COPPER

|

1 OZ

|

ROUTING

|

|

DIELECTRIC

|

FR-4

|

33.O8MIL

|

|

|

L4-INNER

|

CONDUCTOR

|

COPPER

|

1 OZ

|

ROUTING

|

|

DIELECTRIC

|

FR-4

|

5.910MIL

|

|

|

L5-INNER

|

CONDUCTOR

|

COPPER

|

1 OZ

|

PLANE

|

|

DIELECTRIC

|

FR-4

|

3.800MIL

|

|

|

BOTTOM

|

CONDUCTOR

|

COPPER

|

0.5 OZ

|

ROUTING

|

|

SURFACE

|

AIR

|

|

|

ЫЕУїЃКжаМфИїВуМфЕФЕчНщжЪЮЊFR-4ЃЌЦфНщЕчГЃЪ§ЮЊ4.2ЃЛЖЅВуКЭЕзВуЮЊТуВуЃЌжБНггыПеЦјНгДЅЃЌПеЦјЕФНщЕчГЃЪ§ЮЊ1ЁЃ

ашвЊНјаазшПЙПижЦЕФаХКХЮЊЃК

DDRЕФЪ§ОнЯпЃЌЕЅЖЫзшПЙЮЊ50ХЗФЗЃЌзпЯпВуЮЊTOPКЭL2ЁЂL3ВуЃЌзпЯпПэЖШЮЊ5milЁЃ

ЪБжгаХКХCLKКЭUSBЪ§ОнЯпЃЌВюЗжзшПЙПижЦдк100ХЗФЗЃЌзпЯпВуЮЊL2ЁЂL3ВуЃЌзпЯпПэЖШЮЊ6milЃЌзпЯпМфОрЮЊ6milЁЃ

ЖдгкМЦЫуОЋЖШЕФЫЕУї:

1ЁЂЖдгкЕЅЖЫзшПЙПижЦЃЌМЦЫужЕЕШгкПЭЛЇвЊЧѓжЕЃЛ

2ЁЂЖдгкЦфЫћЬиадзшПЙПижЦЃК

ЖдгкЦфЫќЫљгаЕФзшПЙЩшМЦ(АќРЈВюБ№КЭЬиадзшПЙ)

*МЦЫужЕгыУћвхжЕВюБ№гІаЁгкЕФзшПЙЗЖЮЇЕФ10%ЃК

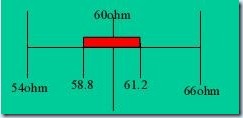

Р§ШчЃКПЭЛЇвЊЧѓЃК60+/-10%ohm

зшПЙЗЖЮЇ=ЩЯЯо66-ЯТЯо54=12ohms

зшПЙЗЖЮЇЕФ10%=12X10%=1.2ohms

МЦЫужЕБиаыдкКьПђЗЖЮЇФкЁЃЦфгрЧщПіРрЭЦЁЃ

ЯТУцРћгУSI9000МЦЫуЪЧЗёДяЕНзшПЙПижЦЕФвЊЧѓЃК

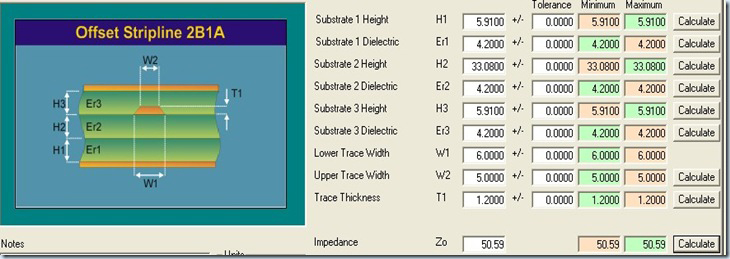

ЪзЯШМЦЫуDDRЪ§ОнЯпЕФЕЅЖЫзшПЙПижЦЃК

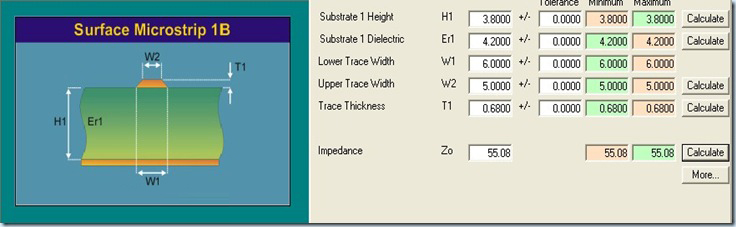

TOPВуЃКЭКёЮЊ0.5OZЃЌзпЯпПэЖШЮЊ5MILЃЌОрВЮПМЦНУцЕФОрРыЮЊ3.8MILЃЌНщЕчГЃЪ§ЮЊ4.2ЁЃбЁдёФЃаЭЃЌДњШыВЮЪ§ЃЌбЁдёlossless calculation,ШчЭМЫљЪОЃК

МЦЫуЕУЕНЕЅЖЫзшПЙЮЊZo=55.08ohmЃЌгывЊЧѓЯрВю5ХЗФЗЁЃИљОнАхГЇЕФЗДРЁЃЌЫћУЧНЋзпЯпПэЖШИФЮЊ6MILвдДяЕНзшПЙПижЦЃЌОЙ§бщжЄЃЌдкПэЖШW2=6MIL,W1=7MILЕФЧщПіЯТЃЌМЦЫуЕУЕНЕФЕЅЖЫзшПЙЮЊZo=50.56ХЗФЗЃЌЗћКЯЩшМЦвЊЧѓЁЃ

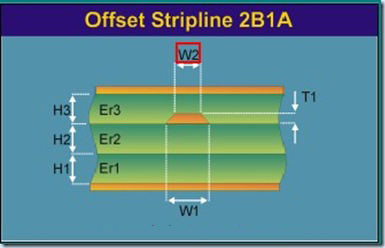

L2ВуЃКдкL2ВуЕФзпЯпФЃаЭШчЯТЭМЫљЪОЃК

ДњШыВЮЪ§НјааМЦЫуЕУЕНШчЯТЭМЫљЪОЃК

МЦЫуЕУЕНЕЅЖЫзшПЙЮЊZo=50.59ХЗФЗЃЌЗћКЯЩшМЦвЊЧѓЁЃ

ЭЌРэПЩвдЕУЕНL3ВуЕФЕЅЖЫзшПЙЃЌдкДЫВЛдйзИЪіЁЃ

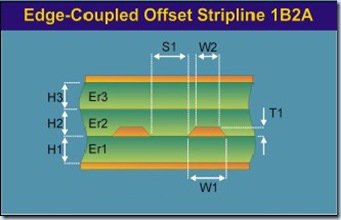

ЯТУцМЦЫуВюЗжзшПЙПижЦЃК

гЩPCBЩшМЦПЩжЊЃЌЕзАхPCBжаЪБжгзпЯпдкL3ВуЃЌUSBЪ§ОнЯпдкL2ВуЃЌзпЯпПэЖШОљЮЊ6MIL,МфОрЮЊ6MILЁЃ

ЪБжгаХКХбЁдёЕФФЃаЭШчЯТЫљЪОЃК

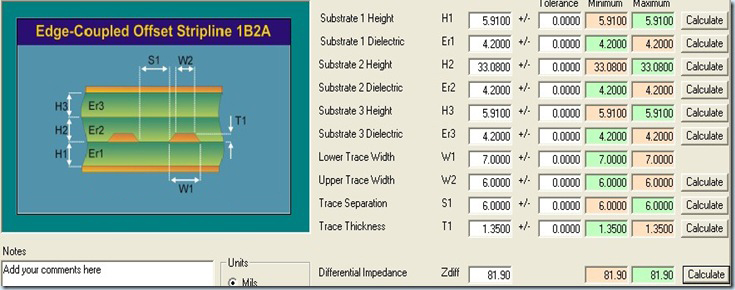

АДееЬсЙЉИјАхГЇЕФЪ§ОнМЦЫуЕУЕНЕФНсЙћШчЯТЭМЫљЪОЃК

ИљОнАхГЇЕФЗДРЁЃЌВюЗжзшПЙжЛФмзіЕН85ХЗФЗЃЌгыМЦЫуНсЙћНгНќЃЈЫћУЧПЩвдЮЂЕїАхВуКёЖШЃЌЕЋВЛФмЕїЯпЃЉЁЃЕЋЪЧИФБфЯпМфОрЮЊ12MILЪБЃЌМЦЫуЕУЕНЕФВюЗжзшПЙЮЊ92.97ХЗФЗЃЌдйНЋЯпПэЕїЮЊ5MILЪБЃЌВюЗжзшПЙЮЊ98.99ХЗФЗЃЌЛљБОЗћКЯЩшМЦвЊЧѓЁЃ

ОбщаЁНс

1ЁЂЕБВюЗжзпЯпдкжаМфаХКХВузпЯпЪБЃЌВюЗжзшПЙЕФПижЦБШНЯРЇФбЃЌвђЮЊОЋЖШВЛЙЛЃЌОЭЪЧЫЕИФБфНщжЪВуКёЖШЖдВюЗжзшПЙЕФгАЯьВЛДѓЃЌжЛгаИФБфзпЯпЕФМфОрВХЖдВюЗжзшПЙгАЯьНЯДѓЁЃЕЋЪЧЕБзпЯпдкЖЅВуЛђЕзВуЪБЃЌВюЗжзшПЙОЭБШНЯКУПижЦЃЌКмШнвзДяЕНЩшМЦвЊЧѓЃЌЭЈЙ§ЪЕМЪМЦЫуЗЂЯжЃЌживЊЕФаХКХЯпзюКУзпБэВуЃЌШнвзНјаазшПЙПижЦЃЌгШЦфЪЧЪБжгаХКХВюЗжЖдЁЃ

2ЁЂдкPCBЩшМЦжЎЧАЃЌЪзЯШБиаыЭЈЙ§зшПЙМЦЫуЃЌАбPCBЕФЕўВуВЮЪ§ШЗЖЈЃЌШчИїВуЕФЭКёЃЌНщжЪВуЕФКёЖШЕШЕШЃЌЛЙгаВюЗжзпЯпЕФПэЖШКЭМфОрЖМашвЊЪТЯШМЦЫуЕУГіЃЌетаЉОЭЪЧPCBЕФЧАЖЫЗТецЃЌБЃжЄживЊЕФаХКХЯпЕФзшПЙПижЦТњзуЩшМЦвЊЧѓЁЃ

3ЁЂЙигкНщЕчГЃЪ§ErЕФЮЪЬтЃК

вдЮвУЧЪЙгУзюЖрЕФFR-4НщжЪЕФВФСЯАхЮЊР§ЃКЪЕМЪЖрВуАхЪЧаОАхКЭбЙКЯЪїжЌВуЖбЕўЖјГЩЃЌЦфаОАхБОЩэвВЪЧгЩАыЙЬЛЏЦЌзщКЯЖјГЩЁЃГЃгУЕФШ§жжАыЙЬЛЏЦЌММЪѕжИБъШчЯТБэ1 ЫљЪОЁЃ

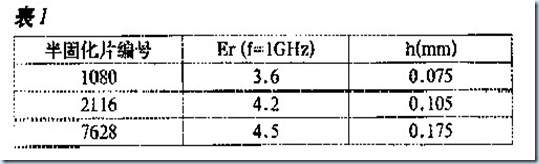

АыЙЬЛЏЦЌзщКЯЕФНщЕчГЃЪ§ВЛЪЧМђЕЅЕФЫуЪѕЦНОљЃЌЩѕжСдкЙЙГЩЮЂДјЯпКЭДјзДЯпЪБЕФErжЕвВгаЫљВЛЭЌЁЃСэвЛЗНУцЃЌFR-4ЕФErвВЫцаХКХЦЕТЪЕФБфЛЏгавЛЖЈИФБфЃЌВЛЙ§дк1GHz вдЯТвЛАуШЯЮЊFR-4 ВФСЯЕФEr жЕдМ4.2ЁЃЭЈГЃМЦЫуЪБВЩгУ4.2ЁЃ

4ЁЂдкЪЕМЪЕФзшПЙПижЦжаЃЌвЛАуВЩгУНщжЪЮЊFR-4ЃЌЦфErдМ4.2ЃЌЯпЬѕКёЖШtЖдзшПЙгАЯьНЯаЁЃЌЪЕМЪжївЊПЩвдЕїећЕФЪЧHКЭWЃЌW(ЩшМЦЯпПэ)вЛАуЧщПіЯТЪЧ гЩЩшМЦШЫдБОіЖЈЕФЃЌЕЋдкЩшМЦЪБгІГфЗжПМТЧЯпПэЖдзшПЙЕФХфКЯадКЭЪЕМЪМгЙЄОЋЖШЁЃЕБШЛЃЌВЩгУНЯаЁЕФW жЕКѓЯпЬѕКёЖШt ЕФгАЯьОЭВЛШнКіЪгСЫЁЃH(НщжЪВуКёЖШ)ЖдзшПЙПижЦЕФгАЯьзюДѓЃЌЪЕМЪH гаСНРрЧщПіЃКвЛжжЪЧаОАхЃЌВФСЯЙЉгІЩЬЫљЬсЙЉЕФАхВФжаHЕФКёЖШвВЪЧгЩвдЩЯШ§жжАыЙЬЛЏЦЌзщКЯЖјГЩЃЌЕЋЦфдкзщКЯЕФЙ§ГЬжаБиШЛЛсПМТЧШ§жжВФСЯЕФЬиадЃЌЖјОјЗЧЮоЬѕМў ЕФШЮвтзщКЯЃЌвђДЫАхВФЕФКёЖШОЭгаСЫвЛЖЈЕФЙцЖЈЃЌаЮГЩСЫвЛИіЯргІЕФЧхЕЅЃЌЭЌЪБH вВгаСЫвЛЖЈЕФЯожЦЁЃШч0.17mm 1/1ЕФаОАхЮЊ 2116 ЁС1ЃЌ0.4mm 1/1ЕФаОАхЮЊ1080ЁС2+7628ЁС1ЕШЁЃСэвЛжжЪЧЖрВуАхжабЙКЯВПЗжЕФКёЖШЃКЦфЗНЗЈЛљБОЩЯгыЧАЯрЭЌЕЋашзЂвтЭВуЕФЫ№ЪЇЁЃШчФкЕчВуМфгУАыЙЬЛЏЦЌНјааЬю ГфЃЌвђдкжЦзїФкВуЕФЙ§ГЬжаЭВБЛЪДПЬЕєЕФВПЗжКмЩйЃЌдђАыЙЬЛЏЦЌжаЪїжЌЖдИУЧјЕФЬюГфврКмЩйЃЌдђАыЙЬЛЏЦЌЕФКёЖШЫ№ЪЇПЩКіТдЁЃЗДжЎЃЌШчаХКХВужЎМфгУАыЙЬЛЏЦЌНјаа ЬюГфЃЌгЩгкЭВБЛЪДПЬЕєЕФВПЗжНЯЖрЃЌдђАыЙЬЛЏЦЌЕФКёЖШЫ№ЪЇЛсКмДѓЧвФбвдЙРМЦЁЃвђДЫЃЌгаШЫНЈвщдкФкВуЕФаХКХВувЊЧѓЦЬЭвдМѕЩйКёЖШЫ№ЪЇЁЃЃЈЩЯЪізЪСЯРДдДгкЃКP C B ИпЫйЪ§зжЩшМЦжаЕФзшПЙПижЦЃЈЮїФЯЕчзгЕчаХММЪѕбаОПЫљ ГТЗЩЃЉЃЉ

5ЁЂЬиеїзшПЙгыДЋЪфЯпЕФПэЖШЪЧГЩЗДБШЕФ,ПэЖШдНПэЃЌзшПЙдНЕЭ,ЗДжЎдђзшПЙИќИпЁЃ

6ЁЂдкгааЉАхЕФЩшМЦвЊЧѓжаЖдАхВуКёЖШгаЯожЦЪБЃЌДЫЪБвЊДяЕНБШНЯКУЕФзшПЙПижЦЃЌВЩгУКУЕФЕўВуЩшМЦЗЧГЃЙиМќЁЃДгЪЕМЪЕФМЦЫужаПЩвдЕУГівдЯТНсТлЃК

a. УПИіаХКХВуЖМвЊгаВЮПМЦНУцЯрСк, ФмБЃжЄЦфзшПЙКЭаХКХжЪСП;

b. УПИіЕчдДВуЖМвЊгаЭъећЕФЕиЦНУцЯрСк, ЪЙЕУЕчдДЕФадФмЕУвдНЯКУЕФБЃжЄ;

7ЁЂЙигкВюЗжзпЯпЕФЯпПэКЭМфОрЖдзшПЙПижЦЕФЬжТлЃК

ЭЈЙ§ШэМўМЦЫуЗЂЯжЃЌИФБфВюЗжЖдЕФМфОрЖдзшПЙПижЦЕФгАЯьНЯДѓЃЌЕЋЪЧетРяЩцМАЕНСэвЛИіЮЪЬтЃЌОЭЪЧВюЗжЖдЕФёюКЯЮЪЬтЁЃ

ВюЗжЖдёюКЯЕФжївЊФПЕФЪЧдіЧПЖдЭтНчЕФПЙИЩШХФмСІКЭвжжЙEMIЁЃёюКЯЗжЮЊНєёюКЯЗНЪН( МДВюЗжЖдЯпМфОраЁгкЛђЕШгкЯпПэ) КЭЫЩёюКЯЗНЪНЁЃ

ШчЙћФмБЃжЄжмЮЇЫљгаЕФзпЯпРыВюЗжЖдНЯдЖЃЈБШШчдЖдЖДѓгк3 БЖЕФЯпПэЃЉЃЌФЧУДВюЗжзпЯпПЩвдВЛгУБЃжЄНєУмЕФёюКЯЃЌзюЙиМќЕФЪЧБЃжЄзпЯпГЄЖШЯрЕШМДПЩЁЃЃЈПЩвдВЮМћJohnson ЕФаХКХЭъећадЭјеОЩЯЕФЙигкВюЗжзпЯпЕФВћЪіЃЌЫћОЭвЊЧѓЫћЕФlayout ЙЄГЬЪІНЋВюЗжЯпРыЕУНЯдЖЃЌетбљПЩвдЗНУцШЦЯпЃЉЁЃжЛЪЧФПЧАДѓЖрЪ§ЖрВуИпЫйЕФPCB АхзпЯпПеМфКмНєУмЃЌИљБОЮоЗЈНЋВюЗжзпЯпКЭЦфЫќзпЯпИєРыПЊРДЃЌЫљвдетЪБКђБЃГжНєУмЕФёюКЯвддіМгПЙИЩШХФмСІЪЧгІИУЕФЁЃ

НєёюКЯВЛЪЧВюЗжзпЯпЕФБивЊЬѕМўЃЌЕЋЪЧдкПеМфВЛЙЛЪБзпЯпВЩгУНєёюКЯЗНЪНФмЙЛдіЧПВюЗжзпЯпЕФПЙИЩШХФмСІЁЃвђДЫЃЌЖдгкВюЗжЖдЕФзшПЙПижЦЮЪЬтЃЌдѕУДЕїНкИїИіВЮЪ§ашвЊзлКЯПМТЧЩЯЪівђЫиЃЌдёгХбЁдёЁЃвЛАуЧщПіЯТВЛЧсвзЕїећВюЗжЖдЕФМфОрКЭЯпПэЁЃ

бгЩьЃКВюЗжЖдзпЯпЕФPCBвЊЧѓ

ЃЈ1ЃЉШЗЖЈзпЯпФЃЪНЁЂВЮЪ§МАзшПЙМЦЫуЁЃВюЗжЖдзпЯпЗжЭтВуЮЂДјЯпВюЗжФЃЪНКЭФкВуДјзДЯпВюЗжФЃЪНСНжжЃЌЭЈЙ§КЯРэЩшжУВЮЪ§ЃЌзшПЙПЩРћгУЯрЙизшПЙМЦЫуШэМў(ШчPOLAR-SI9000)МЦЫувВПЩРћгУзшПЙМЦЫуЙЋЪНМЦЫуЁЃ

ЃЈ2ЃЉзпЦНааЕШОрЯпЁЃШЗЖЈзпЯпЯпПэМАМфОрЃЌдкзпЯпЪБвЊбЯИёАДееМЦЫуГіЕФЯпПэКЭМфОрЃЌСНЯпМфОрвЊвЛжББЃГжВЛБфЃЌвВОЭЪЧвЊБЃГжЦНааЁЃЦНааЕФЗНЪНгаСНжжЃК вЛжжЮЊСНЬѕЯпзпдкЭЌвЛЯпВу(side-by-side)ЃЌСэвЛжжЮЊСНЬѕЯпзпдкЩЯЯТЯрСНВу(over-under)ЁЃвЛАуОЁСПБмУтЪЙгУКѓепМДВуМфВюЗжаХКХЃЌ вђЮЊдкPCBАхЕФЪЕМЪМгЙЄЙ§ГЬжаЃЌгЩгкВуЕўжЎМфЕФВубЙЖдзМОЋЖШДѓДѓЕЭгкЭЌВуЪДПЬОЋЖШЃЌвдМАВубЙЙ§ГЬжаЕФНщжЪСїЪЇЃЌВЛФмБЃжЄВюЗжЯпЕФМфОрЕШгкВуМфНщжЪКёЖШЃЌ ЛсдьГЩВуМфВюЗжЖдЕФВюЗжзшПЙБфЛЏЁЃРЇДЫНЈвщОЁСПЪЙгУЭЌВуФкЕФВюЗжЁЃ

ЃЈ3ЃЉ.НєёюКЯддђЁЃ

дкМЦЫуЯпПэКЭМфОрЪБзюКУзёЪиНєёюКЯЕФддђЃЌвВОЭЪЧВюЗжЖдЯпМфОраЁгкЛђЕШгкЯпПэЁЃЕБСНЬѕВюЗжаХКХЯпОрРыКмНќЪБЃЌЕчСїДЋЪфЗНЯђЯрЗДЃЌЦфДХГЁЯрЛЅЕжЯћЃЌЕчГЁЯрЛЅёюКЯЃЌЕчДХЗјЩфвВвЊаЁЕУЖрЁЃ

ЃЈ4ЃЉ.зпЖЬЯпЁЂжБЯпЁЃ

ЮЊШЗБЃаХКХЕФжЪСПЃЌВюЗжЖдзпЯпгІИУОЁПЩФмЕиЖЬЖјжБЃЌМѕЩйВМЯпжаЕФЙ§ПзЪ§ЃЌБмУтВюЗжЖдВМЯпЬЋГЄЃЌГіЯжЬЋЖрЕФЙеЭфЃЌЙеЭфДІОЁСПгУ45ЁуЛђЛЁЯпЃЌБмУт90ЁуЙеЭфЁЃ

ЃЈ5ЃЉ.ВЛЭЌВюЗжЯпЖдМфДІРэЁЃ

ВюЗжЖдЖдзпЯпЗНЪНЕФбЁдёУЛгаЯожЦЃЌЮЂДјЯпКЭДјзДЯпОљПЩЃЌЕЋЪЧБиаызЂвтвЊгаСМКУЕФВЮПМЦНУцЁЃЖдВЛЭЌВюЗжЯпжЎМфЕФМфОрвЊЧѓМфИєВЛФмЬЋаЁЃЌжСЩйгІДѓгк3ЁЋ5БЖВюЗжЯпМфОрЁЃБивЊЪБдкВЛЭЌВюЗжЯпЖджЎМфМгЕиПзИєРывдЗРжЙЯрЛЅЮЪЕФДЎШХЁЃ

ЃЈ6ЃЉ.дЖРыЦфЫќаХКХЁЃ

ЖдВюЗжЖдаХКХКЭЦфЫќаХКХБШШчTTLаХКХЃЌзюКУЪЙгУВЛЭЌЕФзпЯпВуЃЌШчЙћвђЮЊЩшМЦЯожЦБиаыЪЙгУЭЌвЛВузпЯпЃЌВюЗжЖдКЭTTLЕФОрРыгІИУзуЙЛдЖЃЌжСЩйгІИУДѓгк3~5БЖВюЗжЯпМфОрЁЃ

ЃЈ7ЃЉ.ВюЗжаХКХВЛПЩвдПчЦНУцЗжИюЁЃ

ОЁЙмСНИљВюЗжаХКХЛЅЮЊЛиСїТЗОЖЃЌПчЗжИюВЛЛсИюЖЯаХКХЕФЛиСїЃЌЕЋЪЧПчЗжИюВПЗжЕФДЋЪфЯпЛсвђЮЊШБЩйВЮПМЦНУцЖјЕМжТзшПЙЕФВЛСЌај(ШчЭММ§ЭЗДІЫљЪОЃЌЦфжаGND1ЁЂGND2ЮЊLVDSЯрСкЕФЕиЦНУц)ЁЃ

8ЁЂPADS LAYOUTжаВуЖЈвхбЁЯюПЈИїИіВЮЪ§ЕФНтЪЭЫЕУїЃК

![PCBзшПЙПижЦ I6WJ5$GPMD{{IVU95}]$1PX](http://www.hqpcb.com/Public/Theme/Admin/Dwz/js/ueditor/php/upload/78791407486075.jpg)

coatingБэЪОЭПИВВуЃЌШчЙћУЛгаЭПИВВуЃЌОЭдкthickness жаЬю0,dielectricЃЈНщЕчГЃЪ§ЃЉЬю1ЃЈПеЦјЃЉЁЃ

substrateБэЪОЛљАхВуЃЌМДЕчНщжЪВуЃЌвЛАуВЩгУFR-4ЃЌКёЖШЪЧЭЈЙ§зшПЙМЦЫуШэМўМЦЫуЕУЕНЃЌНщЕчГЃЪ§ЮЊ4.2ЃЈЦЕТЪаЁгк1GHzЪБЃЉЁЃ

ЕуЛїWeight(oz)ЯюЃЌПЩвдЩшЖЈЦЬЭЕФЭКёЃЌЭКёОіЖЈСЫзпЯпЕФКёЖШЁЃ

9ЁЂОјдЕВуЕФPrepreg/CoreЕФИХФюЃК

PPЃЈprepregЃЉЪЧжжНщжЪВФСЯЃЌгЩВЃСЇЯЫЮЌКЭЛЗбѕЪїжЌзщГЩЃЌcoreЦфЪЕвВЪЧPPРраЭНщжЪЃЌжЛВЛЙ§ЫћЕФСНУцЖМИВгаЭВЃЌЖјPPУЛгаЃЌжЦзїЖрВуАхЪБЃЌЭЈГЃНЋCOREКЭPPХфКЯЪЙгУЃЌCOREгыCOREжЎМфгУPPеГКЯЁЃ

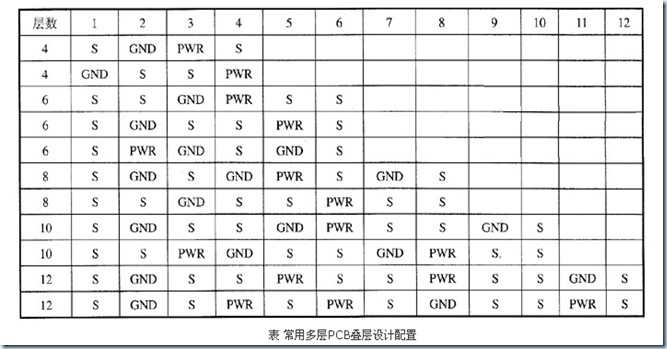

10ЁЂPCBЕўВуЩшМЦжаЕФзЂвтЪТЯюЃК

(1)ЁЂЧЬЧњЮЪЬт

PCBЕФЕўВуЩшМЦвЊБЃГжЖдГЦЃЌМДИїВуЕФНщжЪВуКёЁЂЦЬЭКёЖШЩЯЯТЖдГЦЃЌФУСљВуАхРДЫЕЃЌОЭЪЧTOP-GNDгыBOTTOM-POWERЕФНщжЪКёЖШКЭЭКёвЛжТЃЌGND-L2гыL3-POWERЕФНщжЪКёЖШКЭЭКёвЛжТЁЃетбљдкВубЙЕФЪБКђВЛЛсГіЯжЧЬЧњЁЃ

ЃЈ2ЃЉЁЂаХКХВугІИУКЭСкНќЕФВЮПМЦНУцНєУмёюКЯЃЈМДаХКХВуКЭСкНќЗѓЭВужЎМфЕФНщжЪКёЖШвЊКмаЁЃЉЃЛЕчдДЗѓЭКЭЕиЗѓЭгІИУНєУмёюКЯЁЃ

ЃЈ3ЃЉЁЂдкКмИпЫйЕФЧщПіЯТЃЌПЩвдМгШыЖргрЕФЕиВуРДИєРыаХКХВуЃЌЕЋНЈвщВЛвЊЖрМвЕчдДВуРДИєРыЃЌетбљПЩФмдьГЩВЛБивЊЕФдыЩљИЩШХЁЃ

ЃЈ4ЃЉЁЂЕфаЭЕФЕўВуЩшМЦВуЗжВМШчЯТБэЫљЪОЃК

ЃЈ5ЃЉЁЂВуЕФХХВМвЛАуддђЃК

дЊМўУцЯТУцЃЈЕкЖўВуЃЉЮЊЕиЦНУцЃЌЬсЙЉЦїМўЦСБЮВувдМАЮЊЖЅВуВМЯпЬсЙЉВЮПМЦНУцЃЛ

ЫљгааХКХВуОЁПЩФмгыЕиЦНУцЯрСкЃЛ

ОЁСПБмУтСНаХКХВужБНгЯрСкЃЛ

жїЕчдДОЁПЩФмгыЦфЖдгІЕиЯрСкЃЛ

МцЙЫВубЙНсЙЙЖдГЦЁЃ

ЖдгкФИАхЕФВуХХВМЃЌЯжгаФИАхКмФбПижЦЦНааГЄОрРыВМЯпЃЌЖдгкАхМЖЙЄзїЦЕТЪдк50MHZ вдЩЯЕФ

ЃЈ50MHZ вдЯТЕФЧщПіПЩВЮееЃЌЪЪЕБЗХПэЃЉЃЌНЈвщХХВМддђЃК

дЊМўУцЁЂКИНгУцЮЊЭъећЕФЕиЦНУцЃЈЦСБЮЃЉЃЛ

ЮоЯрСкЦНааВМЯпВуЃЛ

ЫљгааХКХВуОЁПЩФмгыЕиЦНУцЯрСкЃЛ

ЙиМќаХКХгыЕиВуЯрСкЃЌВЛПчЗжИюЧјЁЃ